- 您现在的位置:买卖IC网 > Sheet目录312 > AT25320AY6-10YH-1.8 (Atmel)IC EEPROM 32KBIT 20MHZ 8DFN

Table 3-6.

Address Key

Address

A N

Don’t Care Bits

AT25080A

A 9 –A 0

A 15 –A 10

AT25160A

A 10 –A 0

A 15 –A 11

AT25320A

A 11 –A 0

A 15 –A 12

AT25640A

A 12 –A 0

A 15 –A 13

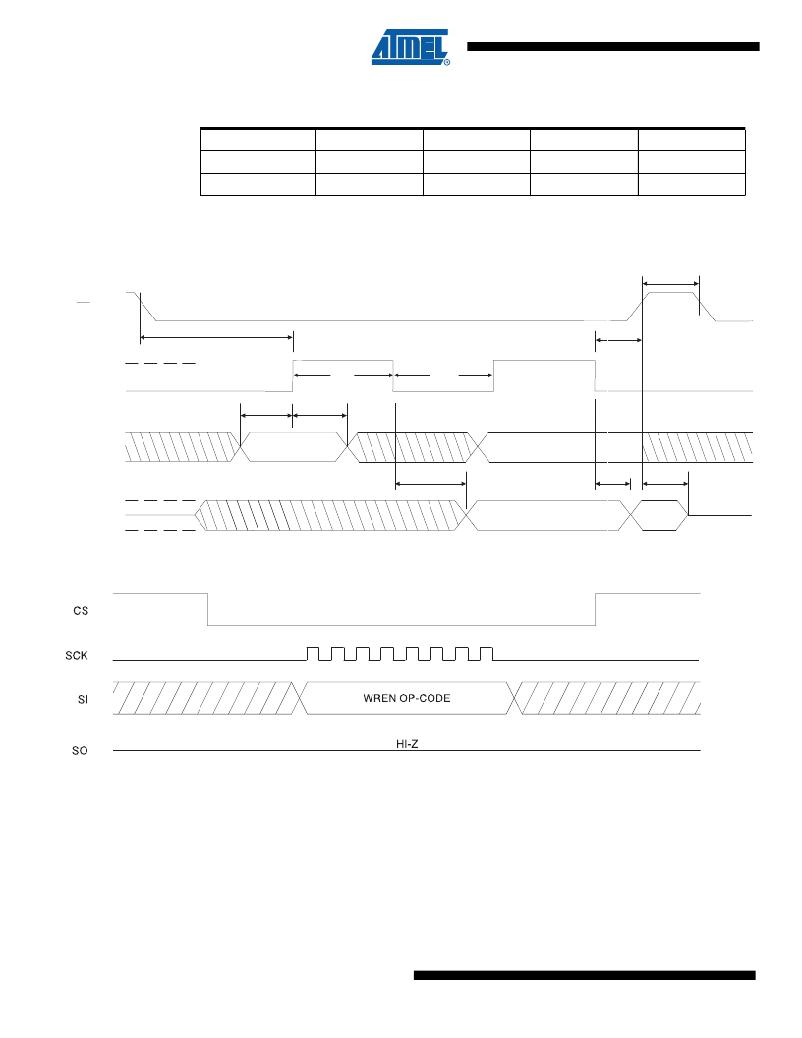

4. Timing Diagrams

Figure 4-1.

V IH

CS

V IL

Synchronous Data Timing (for Mode 0)

t CS

t CSS

V IH

t CSH

SCK

SI

V IL

V IH

V IL

t SU

VALID IN

t WH

t H

t WL

t V

t HO

t DIS

SO

V OH

HI-Z

HI-Z

V OL

Figure 4-2.

WREN Timing

12

AT25080A/160A/320A/640A

3347L–SEEPR–06/07

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

AT25640T1-10TI-2.7

IC EEPROM 64KBIT 3MHZ 14TSSOP

AT25DF321-SU

IC FLASH 32MBIT 70MHZ 8SOIC

AT25F1024AN-10SU-2.7

IC FLASH 1MBIT 33MHZ 8SOIC

AT25F2048N-10SU-2.7

IC FLASH 2MBIT 33MHZ 8SOIC

AT25F4096W-10SU-2.7

IC FLASH 4MBIT 33MHZ 8SOIC

AT25HP512W2-10SI-2.7 SL383

IC EEPROM 512KBIT 10MHZ 16SOIC

AT26DF081A-SSU

IC FLASH 8MBIT 70MHZ 8SOIC

AT26DF161-SU

IC FLASH 16MBIT 66MHZ 8SOIC

相关代理商/技术参数

AT25320B

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:serial electrically-erasable programmable read-only memory

AT25320B_10

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:serial electrically-erasable programmable read-only memory

AT25320B-CUL-T

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:serial electrically-erasable programmable read-only memory

AT25320BD3-DH-T

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:SPI Serial EEPROMs 32K (4096 x 8) 64K (8192 x 8)

AT25320B-MAHL-T

功能描述:电可擦除可编程只读存储器 32K Density SPI 4,096 x 8 Organ RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

AT25320B-MEHL-T

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:serial electrically-erasable programmable read-only memory

AT25320BN-SH-B

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:SPI Serial EEPROMs 32K (4096 x 8) 64K (8192 x 8)

AT25320BN-SH-T

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:SPI Serial EEPROMs 32K (4096 x 8) 64K (8192 x 8)